It can be tricky to infer block RAM, and therefore some engineers prefer to instantiate it instead. You are most likely to hear the term “inferred” to be used with either block RAM or latches.

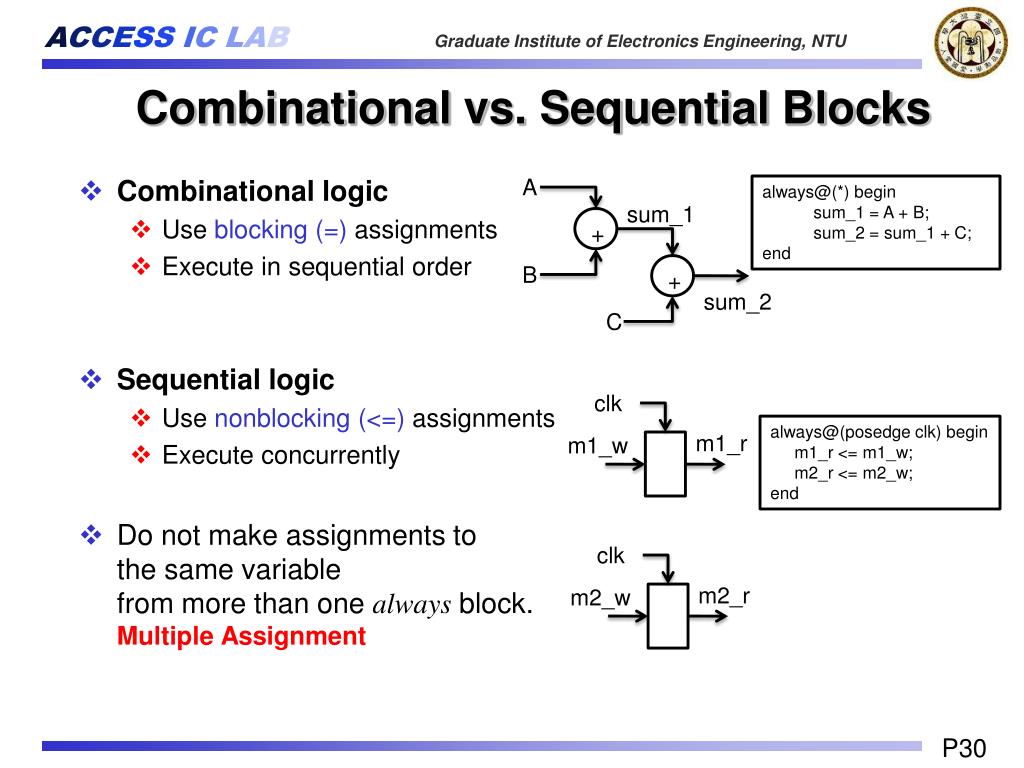

#Combinational vs sequential logic code#

The code below shows a process that will infer a flip-flop. The adept FPGA engineer knows how the synthesis tool “thinks” and can predict that it will map code written a certain way to the desired primitive. The term “to infer” in FPGA design means intentionally describing a specific primitive with HDL code. To learn more about delta cycles in VHDL, I recommend my in-depth article about it: If we turn on Expand Time Deltas Mode in ModelSim, we can observe the delta cycles, as shown below.

#Combinational vs sequential logic simulator#

But behind the scenes, the VHDL simulator uses two delta cycle delays to model the chain of events.

Finally, the last process wakes up and copies the value to sig_c.Īs we can see from the waveform below, the change is instantaneous. The sig_a signal changes from ‘0’ to ‘1’ after ten nanoseconds, causing the second process to wake up and copy the value to sig_b. Consider the example code below with three concurrent VHDL processes. The outputs from a VHDL process with a sensitivity list will have outputs that lag behind the trigger signal with one delta cycle.Ī delta cycle doesn’t consume simulation time. Simultaneous writes to the same address usually result in undefined data.ĭelta cycles are zero-time timesteps used by VHDL simulators for modeling chained events during code execution. While in simple dual-port RAM, one port is for reading and the other for writing, both ports can read and write in true dual-port RAM. True dual-port RAM means that both ports are interchangeable. Therefore, we can use each BRAM primitive individually to store data in our VHDL code. Block RAM is static RAM (SRAM), which doesn’t need refreshing. The CMOS technology in BRAM is different from the dynamic RAM (DRAM) used in regular computer memory.

The image below shows the outline of a dual-port RAM from the Lattice iCE40 FPGA. The term “dual-port” means that it supports simultaneous reads and writes of any two addresses. It can be as little as 32 kbits (Lattice LP640) or as much as 94.5 Mbits (Xilinx VU13P).ĭual-port block RAM is the standard for modern FPGA architectures. The amount of block RAM varies greatly with the price of the FPGA. Usually, the chip provides rows or columns of BRAM distributed evenly throughout the floorplan, as shown in the example for the Lattice iCE40 device below. Block RAM (BRAM) is a type of on-chip random-access memory (RAM) found on most FPGAs.

0 kommentar(er)

0 kommentar(er)